什么是背板?

背板可以用于將多個設備、模塊或電路板連接在一起,實現高速數據傳輸、信號傳輸和控制功能。背板通常具有多個連接器,可以插入不同的模塊或電路板,并通過高速信號線或光纖進行連接。

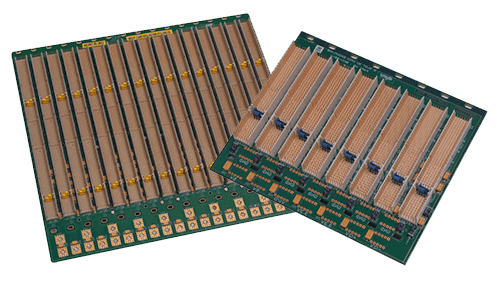

CompactPCI 背板

背板可以提供高帶寬、低延遲、可靠的連接,廣泛應用于通信設備、網絡設備、服務器、計算機等領域。

考慮到背板要承受高頻率、大容量的高速信號傳輸,因此背板PCB在設計時需要考慮到電氣性能、機械性能、可靠性、散熱性能等多個方面,在制造時需要使用高性能的材料,采用高精度的加工工藝,以保證背板PCB能夠達到性能要求并且工作穩定。

背板的板材選型及疊構設計

背板的板材選型

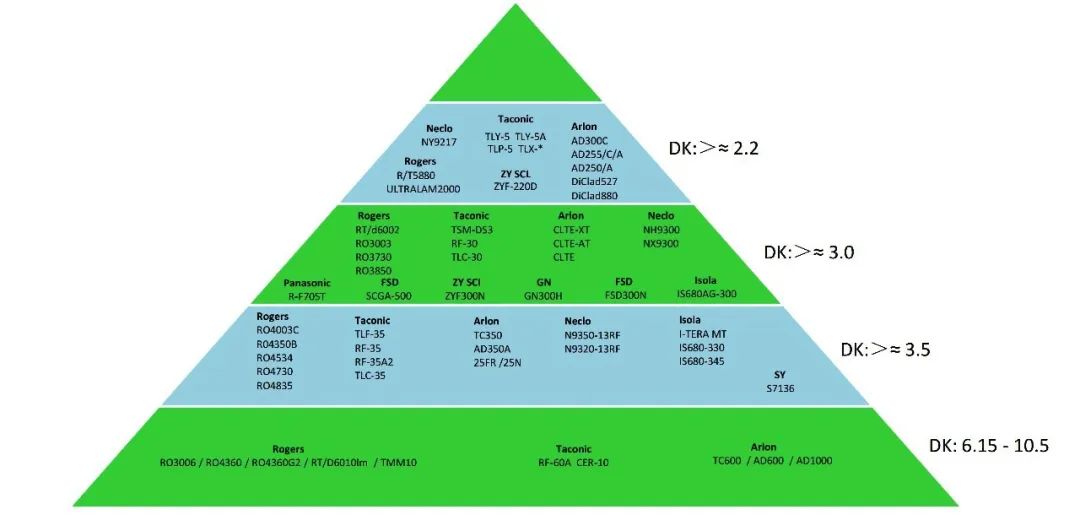

背板通常采用FR4-TG170級別以上的板材,與一般的FR4-TG130相比,玻璃態轉化溫度更高,耐燃性更好,通常選取介電常數ε(Dk)不大于4.4的板材,以減少信號間的串擾。

高速板材選型

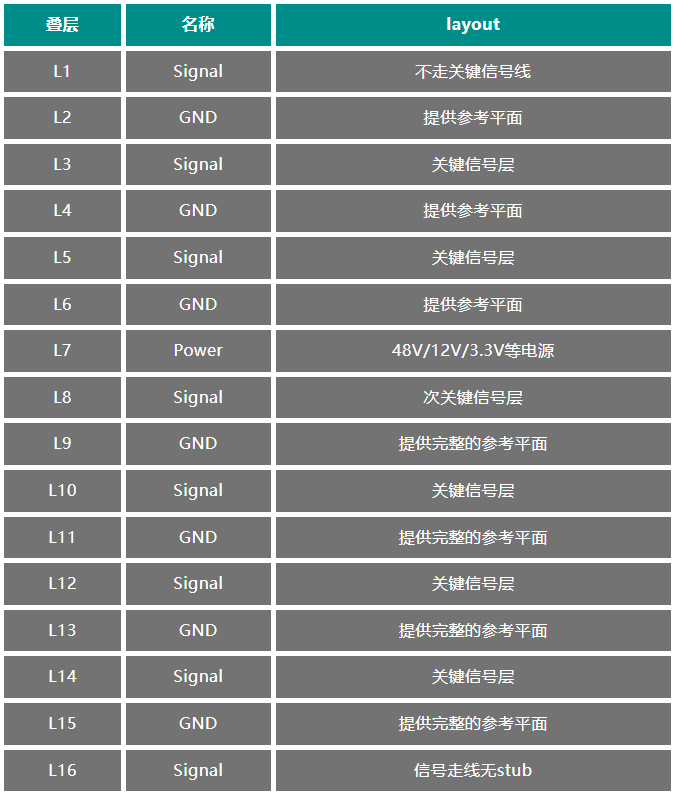

背板的疊層設計

大電流背板的疊層設計

有些背板除了需要考慮多種類型的型號線走線之外,還承載著給各個業務板卡供電的功能。比如OpenVPX 背板,需要承載多種電壓的總電流高達100A。

此時需要使用多個電源平面來滿足電流的需求,可以選擇使用分段策略,在同一層內將電源平面與與高速信號線區域分開布線,如下圖所示。

如果PCB的層數允許,使用地平面將各個電源層隔開,在保證信號線有良好參考平面的同時,能夠保障整個PCB具有良好的屏蔽性。

背板的關鍵信號走線

背板存在3類信號線:時鐘總線、管理總線和高速信號線。

時鐘總線

時鐘總線信號均為差分信號,如M-LVDS電平的多點低電壓差分信號,可以使多個驅動器或接收器共享同一個物理鏈路,時鐘總線設計遵循以下原則 :

時鐘總線源端及末端就近擺放100Ω端接電阻,最大限度地吸收反射信號。

時鐘總線的走線長度不能超過芯片的驅動能力。

時鐘總線經過的過孔盡量不要超過 2 個,減少過孔帶來的寄生電容,過孔附近就近打接地過孔,為交流信號提供最短的回流路徑,每個過孔的出現都會使信號阻抗出現不連續的現象。

時鐘總線間距需采取3W原則,最大程度地減少信號間的串擾。

總線的走線需伴隨有完整的參考平面,保證總線信號回流路徑最短,同時特征阻抗不會發生突變。

差分線的特征阻抗為100Ω。

管理總線

管理總線信號均為單端信號,物理接口形式為I2C,管理總線設計遵循以下原則:

管理總線源端及末端采用就近端接上拉4.7K電阻,提高總線的驅動能力并吸收一部分反射。

管理總線的走線長度不能超過芯片的驅動能力。

單端信號線的特征阻抗設計為65Ω。

高速信號線

高速信號線主要是業務板和交換板之間的數據交換總線和友鄰業務板之間的數據總線,均為高速差分信號線,高速信號線遵循以下設計原則:

差分線經過的過孔盡量不要超過 2個,減少由過孔帶來的寄生電容,并在過孔附近就近打接地過孔,為交流信號提供最短的回流路徑。

差分線需和其他網絡間距采取3W原則,最大程度減少串擾。

差分線的走線需伴隨完整的參考平面,保證總線信號回流路徑最短及特征阻抗不發生突變。

差分線對采用嚴格等長的走線方式,保證差分線對內信號時序穩定。

差分線的特征阻抗設計為100Ω。

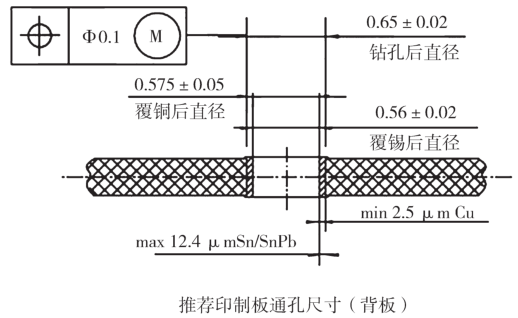

隨著電子封裝、元件和系統向微型化、高密度的方向發展,數據傳輸速率的要求越來越高,連接器逐漸向微間距,多排插針,高密度的方向發展。普通的焊接型連接器已無法滿足設計要求,逐漸被壓接型連接器所替代。壓接連接的失效率要比普通電烙鐵焊接(無熱沖擊、熱損傷)低一個數量級。

壓接工藝是在常溫下將柔性或硬性插針與印制板金屬化孔配合而形成的一種連接,依靠金屬之間的相互作用,在插針與金屬化孔之間形成類似于原子熔融狀態的緊密接觸,實現連接器和印制板導線之間機械和電氣連接。

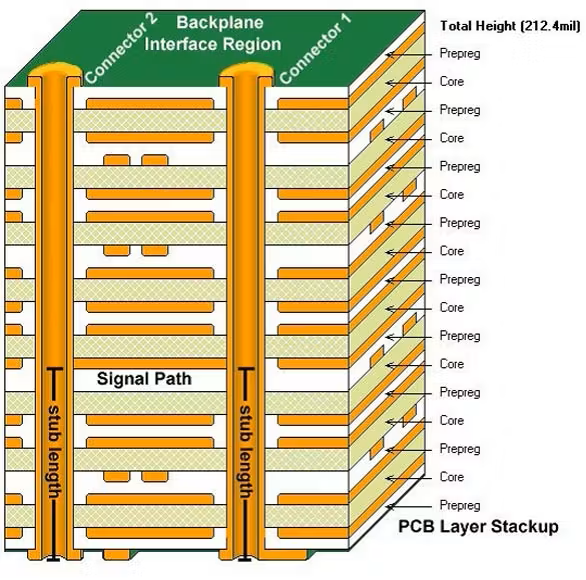

過孔背鉆

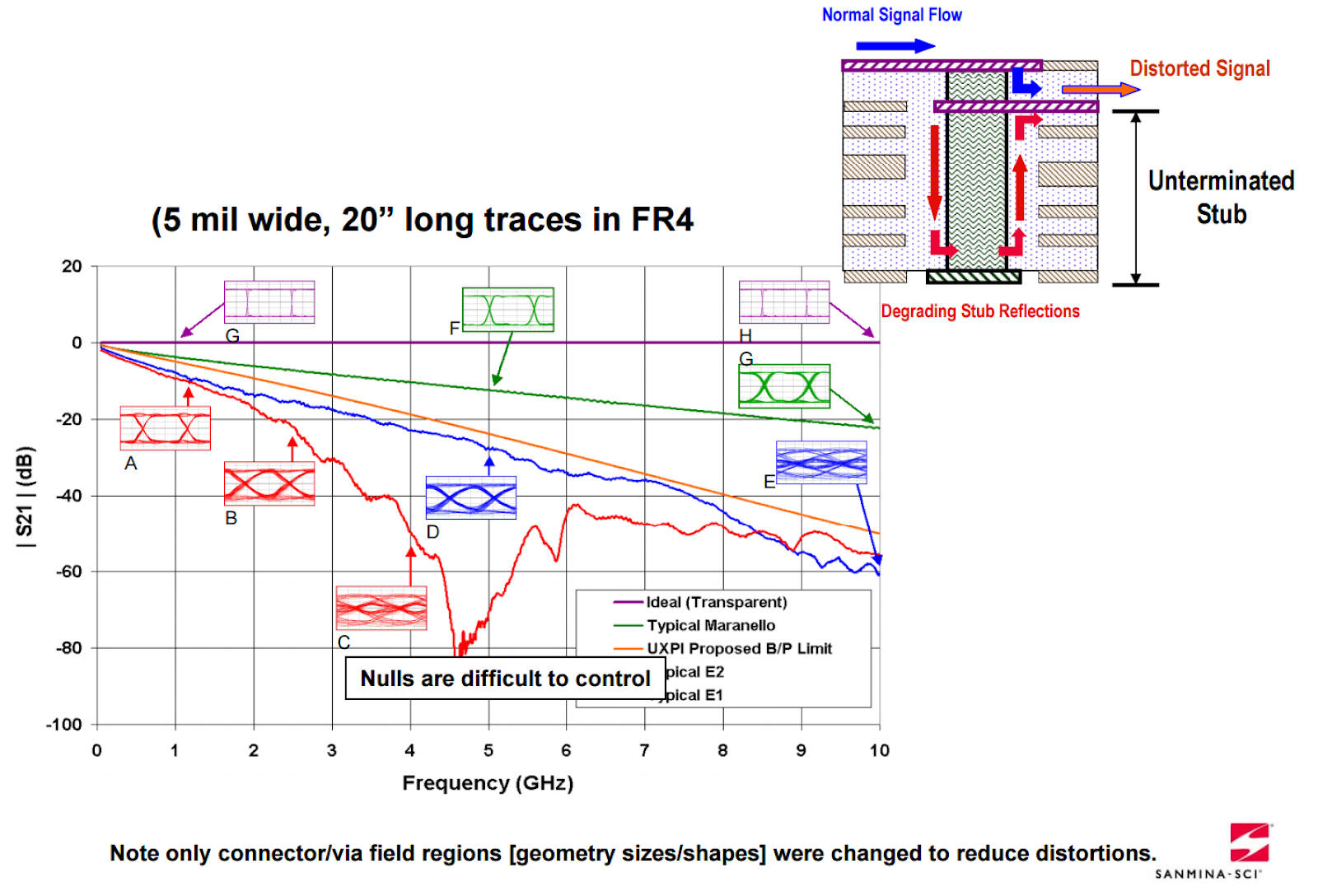

當我們設計好背板,在機箱里面和業務板跑業務測試出現速率跑不上去或者更嚴重的丟包問題時,我們往往會關注業務板與背板之間的連接器,導致阻抗不連續,出現信號完整性問題。但大多時候,阻抗的不連續實際源自過孔。

電鍍通孔(PTH)會讓給高速信號帶來抖動、衰減,產生更高的誤碼率。信號速率越高,電鍍通孔(PTH)帶來的信號失真越大。PTH過孔在6.25Gb/s時的失真通常比在3.125Gb/s時產生的失真大兩倍以上。

過孔殘樁帶來的信號失真

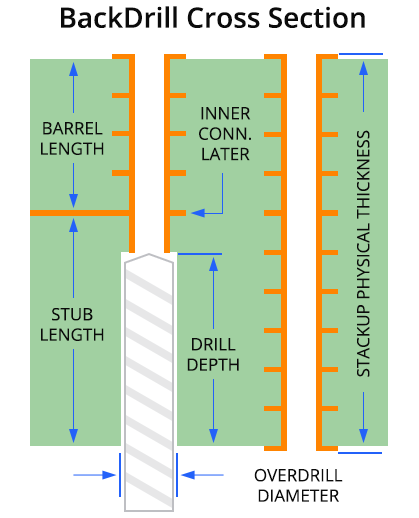

背鉆已被廣泛認為是把過孔對信號衰減降到最低程度簡單而有效的方法。背鉆又被稱為定深鉆孔,采用數控鉆孔設備,通過清除過孔殘段(Stub)。

背鉆使用的鉆頭直徑一般比過孔大大8mil,以便移除不需要的導體殘段。為了保證背鉆不會穿透附近的走線和平面,過孔附近的走線和平面到背鉆孔對應層的間距應該在10mil以上。

背鉆橫截面示意圖

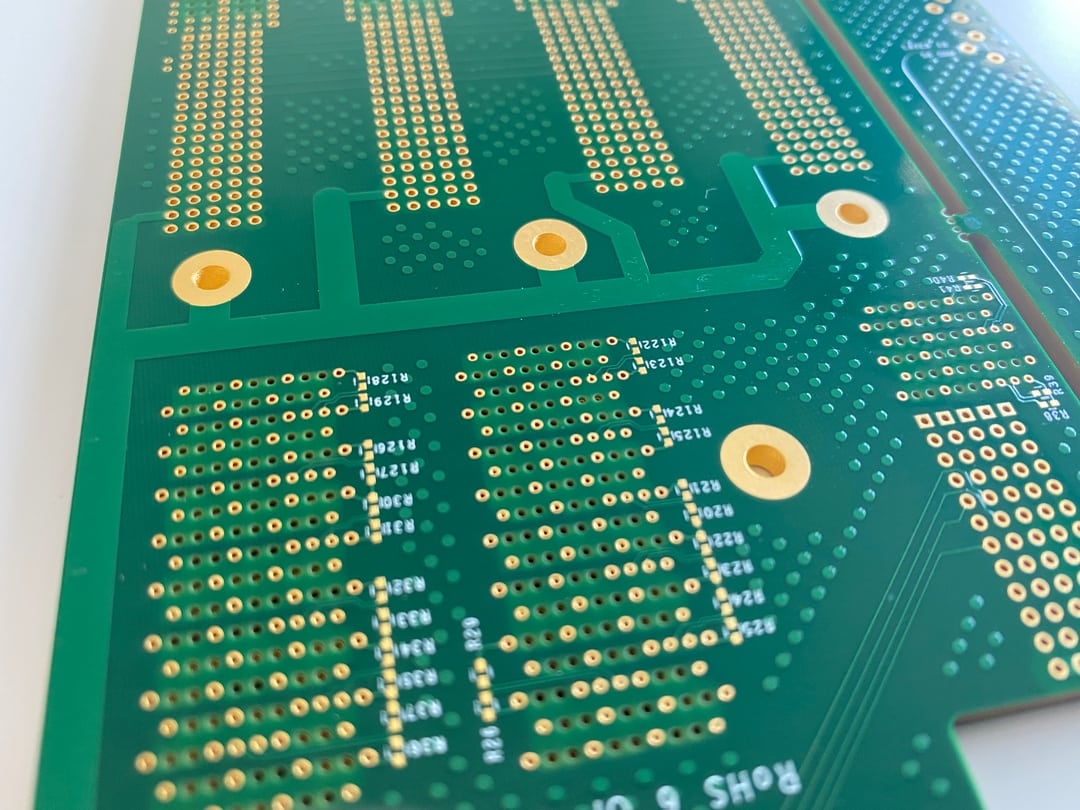

完成背鉆的背板PCB-明陽電路