嵌入式核心板又叫SOM(Systems-on-Module)板,核心板集成了CPU和各種外設(shè),如內(nèi)存(DDR)、存儲(chǔ)(eMMC或FLASH)、電源管理(PMIC)、晶振等。同時(shí)引出如USB、GPIO、SPI、I2C、UART、以太網(wǎng)、PCIe等各種接口,以滿足各種應(yīng)用的需求。

核心板一般采用板對(duì)板連接器、郵票孔焊接、金手指、COM Express等形式與底板連接,并且通常將CPU的所有功能引腳或大部分功能引腳引出,用戶在設(shè)計(jì)產(chǎn)品時(shí)只需根據(jù)應(yīng)用場(chǎng)景進(jìn)行功能接口的電路設(shè)計(jì),從而降低了硬件開發(fā)難度,節(jié)省了開發(fā)時(shí)間。

Intel Atom x6000E COM Express核心板

來自:Congatec

SOM適用于包括工業(yè)自動(dòng)化、醫(yī)療設(shè)備、汽車電子、通信系統(tǒng)和物聯(lián)網(wǎng)(IoT)在內(nèi)的多種行業(yè)。使用SOM,可以大大縮短產(chǎn)品開發(fā)周期,降低綜合成本,提高產(chǎn)品的可靠性。

為了確保嵌入式核心板硬件和軟件的兼容性、模塊化和可擴(kuò)展性。不同組織或公司定義了多個(gè)標(biāo)準(zhǔn),常見的嵌入式核心板標(biāo)準(zhǔn)如下:

Open Standard Module (OSM)

OSM核心板是一個(gè)可焊接的LGA封裝模塊,尺寸緊湊,最大的尺寸為45mm x 45mm,模塊功率通常在15W以下。對(duì)于物聯(lián)網(wǎng)應(yīng)用十分友好,可以滿足低成本和日益增長(zhǎng)的性能需求。

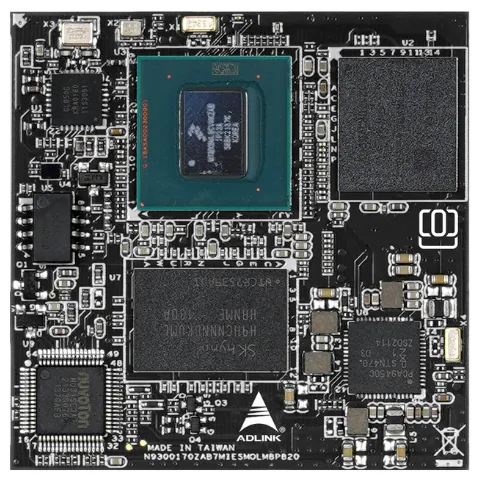

OSM標(biāo)準(zhǔn)的IMX8MP 核心板

來自:ADLINK

QSeven (Q7)

由NXP Semiconductors(原Freescale Semiconductor)推出的一種基于ARM架構(gòu)的嵌入式處理器模塊標(biāo)準(zhǔn)。標(biāo)準(zhǔn)采用230-pin MXM金手指設(shè)計(jì), 便于手持設(shè)備、HMI和標(biāo)牌應(yīng)用中的高速I/O連接。

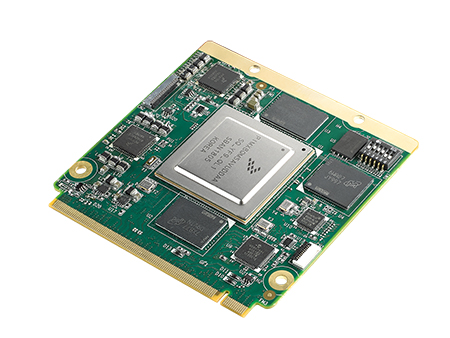

基于NXP i.MX 8QM Qseven 核心板

來自:Advantech

SMARC

SMARC (Standard Module Advanced RISC Computer),是一種用于定義ARM架構(gòu)的嵌入式計(jì)算機(jī)模塊的開放標(biāo)準(zhǔn)。采用314針的MXM金手指連接器,適用于高性能和低功耗要求的產(chǎn)品。

Intel Atom x7000 series (Amston Lake) 核心板

來自:ADLINK

COM Express

由PICMG(PCI Industrial Computer Manufacturers Group)定義的一種模塊化計(jì)算機(jī)標(biāo)準(zhǔn),支持多種處理器架構(gòu),如x86、ARM和PowerPC。COM Express模塊包括Mini、Basic和Compact三種尺寸,可以針對(duì)特定的應(yīng)用和功率來選擇適合的尺寸。

為了適應(yīng)下一代AIoT應(yīng)用,COM Express R3.1新增了多個(gè)高級(jí)接口支持包括Type 6/7/10新增PCIe Gen 4接口,Type 6模塊增加USB 4.0接口,Type 7模塊新增第二個(gè)PCIe Clock,并將10G以太網(wǎng)升級(jí)至支持CEI邊帶信號(hào)。

COM Express Type 6 第11代 Intel Cor i7 核心板

來自:ADLINK

隨著嵌入式處理器的性能越來越高,內(nèi)存速率越來越快,嵌入式核心板的PCB層數(shù)也從早期的4層發(fā)展到了8-12層,由于支持越來越多的高速接口,對(duì)板材損耗的要求也越來越高。

一般遵循以下步驟進(jìn)行嵌入式核心板PCB的設(shè)計(jì):

確定元器件布局

一般來講,核心板標(biāo)準(zhǔn)要求里已經(jīng)規(guī)定了標(biāo)準(zhǔn)的外型和接口,元器件的布局變化不會(huì)很大。一般思路是按照CPU的參考手冊(cè)要求,遵循最優(yōu)的fanout布局設(shè)計(jì),確定CPU、DDR和Flash的布局,再優(yōu)化電源和周圍器件的布局。

確定板厚

常規(guī)的PCB成品厚度為0.5mm、0.8mm、1.0mm、1.2mm、1.6mm、2.0mm、3.2mm、6.4mm等等。一般在核心板的設(shè)計(jì)標(biāo)準(zhǔn)里會(huì)規(guī)定板厚,設(shè)計(jì)時(shí)需遵循相應(yīng)的要求,對(duì)于沒有規(guī)定要求的,從結(jié)構(gòu)可靠性角度可以做厚一些。

確定PCB層數(shù)和劃分功能層

確定總層數(shù)和劃分信號(hào)層、電源層和地層,需要從系統(tǒng)性的角度綜合考慮,是一個(gè)相互妥協(xié)的結(jié)果。首先需要確定層數(shù)能夠滿足布線的需求,其次需要滿足高速信號(hào)線的布線要求,最后考慮電源完整性、EMC和熱設(shè)計(jì)的要求。在滿足功能的前提下,盡量壓縮PCB的層數(shù)。

確定內(nèi)外層銅厚

疊層設(shè)計(jì)時(shí)必須平衡銅箔的厚度,使電源/地平面層銅的厚度滿足載流要求。3oz以上屬于厚銅,常用于高壓、大電流的電力電子產(chǎn)品。

對(duì)于信號(hào)層銅的厚度來講,線寬/線距較小,需要銅盡可能薄才能滿足精確的蝕刻的要求。高速信號(hào)線由于趨膚效應(yīng)的影響,電流只在銅箔表面附近流動(dòng),更厚的銅箔并不會(huì)帶來更好的性能。所以內(nèi)層信號(hào)層的銅厚通常為Hoz,即0.5盎司。

確定阻抗線的分布

核心板上的高速接口信號(hào)線都有阻抗要求,常見的單端50Ω、差分100Ω等。阻抗控制,需要有參考平面,走線的銅厚、介電常數(shù)、線寬、線距都會(huì)影響阻抗。在設(shè)計(jì)時(shí)阻抗線時(shí),在滿足阻抗要求的前提下,盡量壓縮阻抗線出現(xiàn)的層數(shù)。

EDA工具都支持阻抗計(jì)算,可以按照設(shè)計(jì)的疊層結(jié)構(gòu),去調(diào)整走線的參數(shù)。

確定過孔結(jié)構(gòu)

大多數(shù)核心板由于高密度的屬性,都會(huì)使用盲孔和埋孔來優(yōu)化布線空間,盲孔和埋孔也同時(shí)造成了PCB需要多次壓合增加了工序,PCB的制造難度上升,因此也更加昂貴。

在疊層設(shè)計(jì)時(shí),需要在滿足設(shè)計(jì)的前提下,盡量簡(jiǎn)化孔的結(jié)構(gòu)。

選擇滿足設(shè)計(jì)要求的板材、PP和銅箔

FR-4能夠滿足大多數(shù)PCB的需求,價(jià)格便宜而且電氣性能良好,高速PCB會(huì)選用高速板材,比如松下的Megtron4/6等,高速PCB需要選擇具有最低損耗角正切和較小介電常數(shù)的介電材料,來滿足高速信號(hào)對(duì)于損耗的要求。

銅箔粗糙度(銅牙)使線路的寬度、線間距不均勻,從而導(dǎo)致阻抗不可控,同時(shí)由于趨膚效應(yīng),電流集中在導(dǎo)體的表層,銅箔的表面粗糙度影響信號(hào)傳輸?shù)拈L(zhǎng)度。信號(hào)的頻率在5GHz以下時(shí)銅箔粗糙度的影響不是太明顯,大于5GHz時(shí)銅箔粗糙度的影響開始越來越大,在大于10Ghz的高速信號(hào)的設(shè)計(jì)時(shí)尤其需要重視。